Referensi

:

1.

Darwison, 2010, "Teknik Interface (antarmuka) : Perancangan Hardware dan

Simulasi Software Serta Aplikasinya", ISBN:978-602-9081-10-7, CV Ferila,

Padang.

2.

Barry B. Bray, "Mikroprosessor Intel",Jilid 1,Edisi 6.

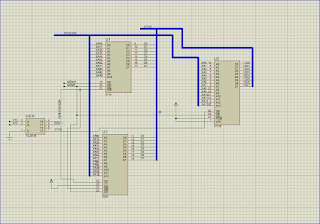

Perancangan sistem minimum 8088 merupakan perancangan peta memori dan peta

Input-Output. Pada sistem minimum 8088 untuk pemetaan memori dan Input-Output dapat

digabung dalam suatu peta atau dapat juga terpisah. Untuk perancangan peta

memori ada dua lokasi address yaitu program disimpan pada lokasi address memori

ROM dan program disimpan pada lokasi address RAM. Biasanya ROM dipakai sebuah

IC ROM tetapi untuk RAM dapat dipakai lebih dari satu IC RAM, misalkan IC RAM

untuk interrupt dan IC RAM untuk data.

1. Peta terpisah

untuk memori dan I-O

1.1

Pemetaan Memori

Perancangan sistem

minimum yang menggunakan 2 RAM dan 1 ROM yaitu RAM 6116 (2 KB)

dan RAM 6264 (8 KB)

dan ROM 27128 (16 KB). Adapun perancangan peta memori ini adalah seperti gambar dibawah.

00000

007FF

|

RAM-0 6116 (2 KB)

|

00800

0FFFF

|

Kosong

|

10000

11FFF

|

RAM-1 6264 (8 KB)

|

12000

FBFFF

|

Kosong

|

FC000

FFFF0

FFFFF

|

ROM 27128 (16 KB)

|

Jump RESET

|

Gambar. Peta Memory

Adapun rangkaian decodernya yang dapat dirancang untuk membedakan RAM

dengan ROM seperti rangkaian pada gambar dibawah.

1.2 Pemetaan Input-Output

Perancangan

menggunakan 4

komponen I-O yaitu PPI-0 8255 dan PPI-1 8255, PIT 8253 serta PIC 8259. Untuk PPI 8255 masing-masing membutuhkan 4 kombinasi address (A1 A0 yaitu 0

s/d 3 Byte), PIT 8253 membutuhkan 4

kombinasi address yaitu A1A0 serta PIC 8259 membutuhkan 2 kombinasi address

yaitu A0. Adapun perancangan peta I-O ini adalah seperti gambar dibawah.

00000

00003

|

PPI-0 8255 (4 B)

|

00004

000FF

|

Kosong

|

00100

00103

|

PPI-1 8255 (4 B)

|

00104

001FF

|

Kosong

|

00200

00203

00204

003FF

|

PIT 8253 (4 B)

|

Kosong

|

|

00400

00401

|

PIC 8259 (2 B)

|

00402

FFFFF

|

Kosong

|

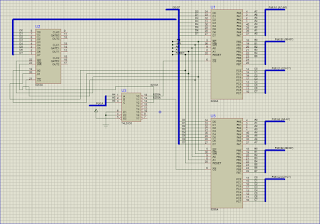

Untuk membedakan PPI-0,

PPI-1, PIT dan PIC dapat dirancang rangkaian decodernya seperti gambar dibawah.

2. Peta gabungan

memori dan Input-Output

Perancangan sistem menggunakan 2 RAM dan 1 ROM yaitu

RAM 6116 (2 KB), RAM

6264 (8 KB) dan

ROM 27128 (16 KB) serta 4 komponen I-O

yaitu PPI-0 8255 dan PPI-1 8255, PIT 8253 serta PIC 8259. Adapun perancangan peta gabungan memori dan

I-O ini adalah seperti gambar dibawah.

00000

007FF

|

RAM-0 6116 (2 KB)

|

00800

0FFFF

|

Kosong

|

10000

10003

|

PPI-0 8255 (4 B)

|

10004

1FFFF

|

Kosong

|

20000

21FFF

|

RAM-1 6264 (8 KB)

|

22000

2FFFF

|

Kosong

|

30000

30003

|

PPI-1 8255 (4 B)

|

30004

3FFFF

|

Kosong

|

40000

40003

|

PIT 8253 (4 B)

|

40004

4FFFF

|

Kosong

|

50000

50001

|

PIC 8259 (2 B)

|

50002

FBFFF

|

Kosong

|

FC000

FFFF0

FFFFF

|

ROM

27128 (16 KB)

|

Jump RESET

|

Untuk membedakan ketujuh komponen memori dan input-output dapat dilihat

pada rangkaian decodernya seperti gambar dibawah,

Untuk penjelasan lebih lengkap dapat mendownload link dibawah ini :

Materi Presentasi

Rangkaian Pada Proteus

Video Simulasi Pembuatan Rangkaian

Materi Presentasi

Rangkaian Pada Proteus

Video Simulasi Pembuatan Rangkaian

bagaimana gambar rangkaian jika menggunakan ppi 8255, ic 2864 (eeprom), dan ic 6116 (rom). mohon bantuannya, terima kasih

BalasHapus